Product Summary

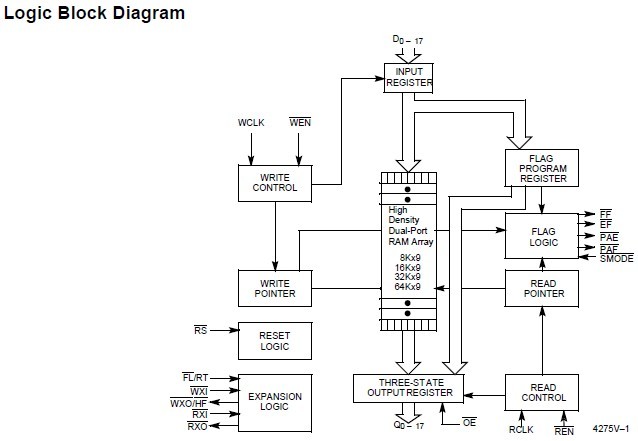

The CY7C4285V-10ASXC is a high speed, low power, first-in first-out (FIFO) memory with clocked read and write interfaces. All are 18 bits wide and are pin and functionally compatible to the CY7C4285V-10ASXC Synchronous FIFO family. The CY7C4285V-10ASXC can be cascaded to increase FIFO depth. Programmable features include Almost Full/Almost Empty flags. The FIFO provides solutions for a wide variety of data buffering needs, including high speed data acquisition, multiprocessor interfaces, and communications buffering. The CY7C4285V-10ASXC has 18-bit input and output ports that are controlled by separate clock and enable signals. The input port is controlled by a free-running clock (WCLK) and a write enable pin (WEN).

Parametrics

CY7C4285V-10ASXC absolute maximum ratings: (1)Storage Temperature: –65 to +150℃; (2)Ambient Temperature with Power Applied: –55 to +125℃; (3)Supply Voltage to Ground Potential: –0.5V to VCC+0.5V; (4)DC Voltage Applied to Outputs in High Z State: –0.5V to VCC + 0.5V; (5)DC Input Voltage Output Current into Outputs (LOW): 20 mA; (6)Static Discharge Voltage: > 2001V (per MIL–STD–883, Method 3015); (7)Latch-Up Current: > 200mA.

Features

CY7C4285V-10ASXC features: (1)3.3 V operation for low power consumption and easy integration into low voltage systems; (2)High speed, low power, first-in first-out (FIFO) memories; (3)8 K × 18 (CY7C4255V); (4)16 K × 18 (CY7C4265V); (5)32 K × 18 (CY7C4275V); (6)64 K × 18 (CY7C4285V); (7)0.35 micron CMOS for optimum speed and power; (8)High speed 100 MHz operation (10 ns read/write cycle times); (9)Low power; (10)Fully asynchronous and simultaneous read and write operation; (11)Empty, Full, Half Full, and programmable Almost Empty and Almost Full status flags; (12)Retransmit function; (13)Output Enable (OE) pin; (14)Independent read and write enable pins; (15)Supports free running 50% duty cycle clock inputs; (16)Width Expansion Capability; (17)Depth Expansion Capability; (18)64-pin 10×10 STQFP; (19)Pin compatible density upgrade to CY7C42X5V-ASC families; (20)Pin compatible 3.3 V solutions.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CY7C4285V-10ASXC |

Cypress Semiconductor |

FIFO 64K X18 LOW VOLTAGE DEEP SYNC FIFO |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

CY7C006 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXCT |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AC |

|

IC SRAM 16KX8 DUAL 64LQFP |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))